基于 DSP 中 EMIF 端口的光栅尺数据采集

2017-8-7 来源:哈尔滨工业大学航天学院 作者:万勇利 魏 凯 韩纪晓 陈兴林

摘 要 : 光栅尺是设备中常用的位置检测装置 , 其测量输出的信号为数字脉冲 , 具有检测范围大 , 检测精度高 , 响应速度快的特点。C6000 系列 DSP 芯片功耗低 , 而且具有高性能的处理能力 , 而且其 EMIF 接口与可以实现与外部存储扩展的无缝连接。本文介绍一种利用 EMIF 与 FPGA 的无缝连接 , 实现 DSP 对 FPGA 中存储的光栅尺数据采集方法。

关键词 :DSP;EMIF;FPGA; 光栅尺 ; 数据采集

1 引言

DSP 芯片 , 也称数字信号处理器 , 是一种特别适合于进行数字信号处理运算的微处理器 , 其主要应用是实时快速地实现各种数字信号处理算法。DSP 有丰富的外设资源 , 其中 EMIF 端口更是满足了DSP 的外部存储扩展和数据交换的需求。通过 EMIF 与外部存储器连接可以实现 DSP 与存储器的无缝连接 , 对于数据有更高效的存取速度 , 而且 64 位数据线有极高的数据吞吐量。DSP内部对 EMIFA 与 EMIFB 进行了统一编址 , 对 EMIF扩展的存储空间都有相应的地址映射 , 通过直接访问相应的地址可以直接获得存储在外部扩展存储器中的数据 , 配置好 EMIF 外设后 , 访问数据十分方便。嵌入式设计中常用作外部 FLASH 扩展、存储扩展及和 FPGA数据交换。

光栅尺 , 也称为光栅尺位移传感器 , 是利用光栅的光学原理工作的测量反馈装置。光栅尺经常应用于闭环伺服系统中 , 可用作直线位移或者角位移的检测。其测量输出的信号为数字脉冲 , 具有检测范围大 , 检测精度高 , 响应速度快的特点。利用光栅尺作为位置传感器可以精确地获得控制对象的位置信息 , 而且光栅尺获得的数据容易处理 , 通过简单的精度计算和初始位置选择就可以得到期望的位置信号。

2 DSP 的 EMIF 端口结构

本文以 TMS320C64x 系列 DSP 进行说明。DSP 的EMIF 接口支持异步存储器接口、同步突发静态存储器接口和同步动态存储器接口 , 支持程序代码访问 64 位宽、32 位宽、16 位宽数据访问。DSP 将 EMIF 接 口 分 为 两 个 部 分 ,EMIFA 和EMIFB, 其中 EMIFA 可以支持 64 位、32 位、16 位和8 位数据访问 ,EMIFB 支持 16 位和 8 位数据访问。

DSP 将 EMIF 接 口 分 为 两 个 部 分 ,EMIFA 和EMIFB, 其中 EMIFA 可以支持 64 位、32 位、16 位和8 位数据访问 ,EMIFB 支持 16 位和 8 位数据访问两

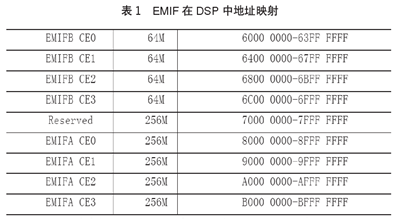

两个 EMIF 端口的存储区均被分为 4 个片选空间 , 都可以单独进行设置与扩展。DSP 对外设 EMIF 端口进行统一编址[1], 其地址映射如表 1 所示。

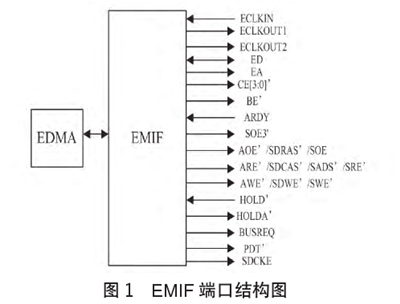

从图中可以看出 EMIFA 和 EMIFB 分别被分为四个片选区 CE0~CE3, 并且分别分配了地址 , 这样使得 DSP可以同时与不同的存储器扩展 , 通过访问不同的地址区即可访问相应的外部存储器 , 大大提高了 EMIF 端口的设计灵活性又提高了 EMIF 端口的使用效率。EMIF 的端口结构[2]如图 1 所示。

ECLKIN:EMIF 的外部时钟输入 , 可以作为 EMIF对外输出时钟频率。

ECLKOUTn:EMIF 对外输出时钟频率 , 它的选择基于 EMIF 的输入时钟频率(1/4 或 1/6 的 DSP 内部时钟频率、外部时钟频率)。其中 ECLKOUT1 频率等于 EMIF 输入时钟频率。ECLKOUT2 可以编程设置为EMIF 输入频率的 1 倍、1/2 或 1/4。时钟频率的选择影响外部存储扩展存储速度 , 配置 EMIF 需要注意。

ED:EMIF 的数据线。

EA:EMIF 的地址线。

对于 EMIF 的外部存储 , 它的两个部分 EMIFA 和EMIFB 可以选择不同的数据位 , 对于 EMIFA 的外部数据线位数选择[2]。EMIFA 的数据线可以选择 64 位 ,32位 ,16 位和 8 位 , 设计相当的灵活 , 可以根据扩展的存储芯片的类型进行选择。EMIFB 的数据线可以选择16 位和 8 位 , 利用 EMIFB 可以进行低数据外部存储的扩展。

EMIFA 常用于与外部传感器进行大量的数据交换 ,而 EMIFB 则可以用作 DSP 芯片的 FLASH 芯片扩展及外部 RAM 扩展。两部分相结合 , 可以满足数据存储交换的需求。

3 EMIF 端口与 FPGA 硬件连接设计

对于 EMIF 端口的引脚我们需要将其与 FPGA 的通用引脚连接起来 , 以便在 FPGA 内进行逻辑编程。其实 ,对于 FPGA 用作 EMIF 的存储用不到所有的引脚 , 但是为了方便以后的设计变化 , 我们在原理图中将 EMIF端口的所有引脚均在 FPGA 中分配了引脚。为了防止没有用到的 EMIF 引脚的干扰 , 可以将没有用到的引脚设为高阻态。本设计以 EMIFA 的端口设计为例进行介绍 ,EMIFB 端口可同样道理进行设计。在 Altium Designer 软件中绘制原理图。图 3 为与EMIF 端口相关元件图。左侧为 DSP 芯片的 EMIF 引脚分布 , 右侧为 FPGA 与 EMIF 相接管脚。将 DSP 与 FPGA 对应管脚相连 , 如图 2 所示结构。

图 2 EMIFA 与 FPGA 连接图

4 DSP 中EMIF 程序配置

在 DSP 中对 EMIF 端口的控制可由 EMIF 对应的寄存器进行配置 , 然后利用 DSP 的库函数应用配置。以EMIFA端口配置为例进行介绍。在DSP中有如下宏定义:

#define EMIFA_FMKS(REG,FIELD,SYM)\

_ P E R _ F M K S ( E M I F A , # # R E G , # #

FIELD,##SYM)

此宏定义可以实现对于 EMIFA 的 REG 寄存器的FIELD 位赋予 SYM 值。这样可以方便的对 EMIFA 寄存器进行配置。对于本设计 ,EMIF 只要控制好数据线和地址线及片选使能信号、读写控制信号即可, 其他的配置可以从简。以下只给出本设计的一些关键配置 ,其参数可以自行调节。其他配置位可以根据技术手册进行设置。

(1) 对于 ENIF 全局控制寄存器 GBLCTL 配置

E M I F A _ F M K S ( G B L C T L , E K2R A T E , HALFCLK) //ECLKOUT2 输出频率为 1/2EMIF 输入时钟频率。

EMIFA_FMKS(GBLCTL, EK2HZ, CLK) //ECLKOUT2 输出不间断EMIFA_FMKS(GBLCTL, EK2EN, ENABLE) //ECLKOUT2 输出使能EMIFA_FMKS(GBLCTL, NOHOLD, DISABLE) // NOHOLD 关闭 ,FPGA 可以发起对 EMIF 总线占有申请。

(2) 对于 ENIFCE 空间控制寄存器 CECTL 配置

EMIFB_FMKS(CECTL, WRSETUP, OF(2)) // 写信号到来前 , 地址线、片选使能先、位使能等信号能建立、读信号完成后使能芯片需要两个时钟周期。EMIFB_FMKS(CECTL, WRSTRB, OF(6)) // 写信号的宽度为 6 个时钟周期。EMIFB_FMKS(CECTL, WRHLD, OF(2))

//写信号到来后对地址线和字节存储线占用 2 个时钟周期。EMIFB_FMKS(CECTL, RDSETUP, OF(2)) //读信号到来前 , 地址线、片选使能先、位使能等信号能建立、读信号完成后使能芯片需要两个时钟周期。

EMIFB_FMKS(CECTL, RDSTRB, OF(6)) //读信号的宽度为 6 个时钟周期。

EMIFB_FMKS(CECTL, MTYPE, ASYNC64) // 存储接口为 64 位同步接口。EMIFB_FMKS(CECTL, RDHLD, OF(2)) // 读信号到来后对地址线和字节存储线占用 2 个时钟周期。

(3) 其他寄存器配置

由于本设计没有使用 SRAM,SDCTL、SDTIM和 S D E X T 默认设置[3]即可。C E S E C 寄存器也保持默认设置。

(4) 利用库函数应用配置

声明结构体 EMIFA_Config, 并将配置好的寄存器值赋予结构体的各个变量。然后利用库函数void EMIFA_config(EMIFA_Config *config);应用配置即可。

5 光栅尺数据采集设计

光栅尺传感器的读数头将读到的数据汇集到采集卡上 , 采集卡可以实现对多路光栅尺数据的存储 , 且按一定的周期刷新各路光栅尺存储的数据 , 因此 , 我们需要及时的将采集卡中的各路数据取出,送与DSP运算处理。本设计采用 FPGA 作为中间环节 , 首先将采集卡上采集到的数据存入 FPGA 内部的双口 RAM 中 ,DSP 再通过EMIF 从 FPGA 的双口 RAM 中读取数据。

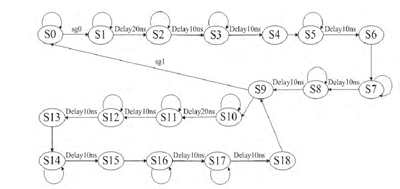

接下来对 FPGA 采集光栅尺数据的逻辑进行设计。由于状态机条理清晰、运行可靠 , 时序容易把握 , 故本设计采用三段式状态机进行设计[4][5]。FPGA 对多路光栅尺数据采集的状态机的状态转移图如图 3 所示。

在 S0 状态 , 判断 5k Hz 上升沿是否到来 , 用此来控制读取光栅尺数据的周期 , 则周期为 200us(远小于采集卡的刷新周期), 由此决定了 DSP 以 200us 为周期处理读到的数据。在 S1 控制发向采集卡的地址和发向双口 RAM 的地址为起始地址 , 延时 20ns, 等待地址线稳定。在 S2 状态 , 将采集卡上得到的数据暂存 , 延时10ns 后 , 在 S3 状态再次读取采集卡同一地址的数据并暂存 , 通过 S4 状态进行数据比较。到 S5, 第三次读取采集卡同一地址的数据并暂存 ,10ns 延时后 , 在 S6 将三次的数据比较 , 得到中间值并暂存。这样使得读数可能存在误码率消除 , 系统更加稳健。在 S7 状态将比较的结果放到双口 RAM 的数据线上 , 并且统计读数次数为 0。延时 10ns, 保证数据线的稳定 , 之后在 S8 状态 , 给双口 RAM 写信号 , 持续 10ns, 保证数据稳定写入。在 S9 状态 , 判断多路光栅尺数据是否读完 , 读完(sg1=1), 则复位 S0 状态 , 否则进入 S10 状态。在S10 状态 , 控制发向采集卡的地址和发向双口 RAM 的地址加 1。S10 到 S18 状态是对采集卡上下一路光栅尺数据的采集 , 原理与前述相同。在 S18 状态 , 读取次数加 1, 回到 S9 状态判断是否读取完毕 , 完毕(sg1=1),则复位 S0, 否则开始下一路光栅尺数据读取。

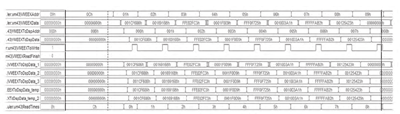

利用 Signal Tap II 对 FPGA 内部逻辑进行监控[6]。可得时序图如图 4 所示。

图 中 ,VMEEXAddr 为 FPGA 向 采 集 卡 发 送的地址 ,VMEEXData 为 FPGA 从采集卡得到的数据。VMEEXTo Dsp Addr 为 FPGA 发向双口 RAM的 地 址 ,VMEEXTo Dsp Data 为 FPGA 发 向 双 口RAM的数据。VMEEXTo Write 为双口 RAM 写信号。Read Times 为读取光栅尺的路数 , 从 0 开始。VMEEXTo Dsp Data_1-3 为三次读取数据的暂存值。从图中可以看出在相应的地址内有效地写入了正确的数据 , 而且实现了多路光栅尺数据的读取 , 时序是正确的。

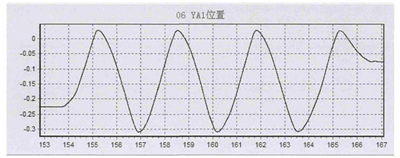

参考图 1 所示统一编址 , 在 DSP 中访问相应的 CE片的地址 ,EMIF 可以自动向 FPGA 中设置的双口 RAM模块发送相应地址 , 取得相应的数据到 DSP, 这样大大简化了访问外部数据的步骤而且又很快的速率。通过上位机监视 DSP 中处理得到的电机运行位置信息 , 可得到如图 5 所示的结果。

图 3 状态机转移图

图 4 光栅尺数据采集时序图

图 5 光栅尺数据采集时序图

由图可见 ,DSP 处理得到了正确的电机位置信息 ,且在运动过程中位置变化平滑无毛刺 , 故本设计达到了正确采集光栅尺数据的要求 , 方案是正确的。

6 结束语

本文设计讨论了一种利用 DSP 的 EMIF 读取多路光栅尺数据的设计方法 , 在实践中得到良好了应用 ,DSP可以准确、可靠地获得光栅尺传感器返回的电机位置信号 , 从而为接下来的控制算法打好基础。在本设计中 , 我们仅讨论利用了 DSP 的 EMIFA 端口 , 对于EMIFB 端口同样可以加以利用 , 可以用来进行 RAM 或FLASH 扩展。设计中 , 利用了 FPGA 作为逻辑处理的中间环节 , 让其将采集卡的数据进行存储 , 这样大大减少了 DSP 的访问压力。由于本文主要针对 TMS32064X系列 DSP 进行了设计 , 对于不同系列 DSP 的 EMIF 配置也有不同 , 故读者在设计时需要加以注意。

投稿箱:

如果您有机床行业、企业相关新闻稿件发表,或进行资讯合作,欢迎联系本网编辑部, 邮箱:skjcsc@vip.sina.com

如果您有机床行业、企业相关新闻稿件发表,或进行资讯合作,欢迎联系本网编辑部, 邮箱:skjcsc@vip.sina.com

更多相关信息